Nvidia 解决芯片制造过程 声称使用 cuLitho 可加快 40 倍

在 GTC 2023 上,Nvidia 宣布了其新的 cuLitho 软件库,用于加速半导体制造工作流程中的一个关键瓶颈。新库加速了计算光刻,这是一种用于为芯片生产创建光掩模的技术。Nvidia 声称其新方法使 500 个 DGX H100 系统使用 4,000 个 Hopper GPU 来完成与 40,000 个基于 CPU 的服务器相同的工作量,但速度提高了 40 倍,功耗降低了 9 倍。Nvidia 声称这将计算光刻工作量从数周减少到八小时来生产光掩模。

芯片制造领导者 TSMC、ASML 和 Synopsys 都已签署新技术,Synopys 已将其集成到其软件设计工具中。随着时间的推移,Nvidia 期望新方法能够实现更高的芯片密度和产量、更好的设计规则以及 AI 驱动的光刻技术。

Nvidia 科学家创建了新算法,允许越来越复杂的计算光刻工作流在 GPU 上并行执行,使用 Hopper GPU 时显示出 40 倍的加速。新算法被集成到一个新的 cuLitho 加速库中,该库可以集成到掩膜制造商的软件中(通常是代工厂或芯片设计师)。cuLitho 加速库也与 Ampere 和 Volta GPU 兼容,但 Hopper 是最快的解决方案。

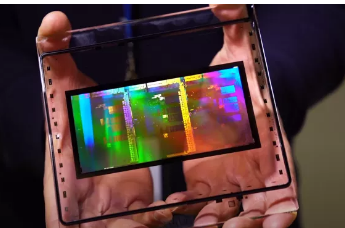

在芯片上打印小特征始于一大块称为光掩模的石英。这种透明石英具有芯片设计的压印图案,其工作方式很像模板——通过掩模照射光线,将设计蚀刻到晶圆上,从而创造出构成现代芯片的数十亿个 3D 晶体管和导线结构。每个芯片设计都需要多次曝光以分层构建芯片设计。因此,芯片制造过程中使用的光掩模数量因芯片而异;它甚至可以超过 100 个口罩。例如,Nvidia 表示制造 H100 需要 89 个掩模,而英特尔引用其 14nm 芯片使用“50+”个掩模。

新技术已经出现,现在允许蚀刻小于用于创建它们的光的波长的特征。然而,特征的持续缩小导致了衍射问题,这实质上“模糊”了印刷到硅片上的设计。计算光刻领域通过优化掩模布局的复杂数学运算来抵消衍射的影响。然而,随着功能进一步缩小,这项任务变得越来越计算密集,从而使每个设计能够增加数十亿个晶体管。

这些复杂的问题需要大型计算机集群,通常有数万台服务器(Nvidia 引用 40,000 台),这些计算机在 CPU 上并行处理工作负载中的数字,处理单个光掩模可能需要长达数周的时间(时间量根据芯片的复杂性而有所不同——英特尔表示其团队需要五天时间来创建一个掩模)。

Nvidia 认为,设计现代掩模所需的服务器数量正以与摩尔定律相同的速度增长,从而将服务器要求和运行它们所需的电量推向不可持续的境地。事实上,新掩模技术的令人难以置信的计算要求,例如使用逆曲线掩模 (ILM) 的逆光刻技术 (ILT)), 已经阻碍了这些更先进技术的采用。此外,高 NA EUV 和 ILT 预计在未来几年将掩模的数据处理量增加 10 倍。